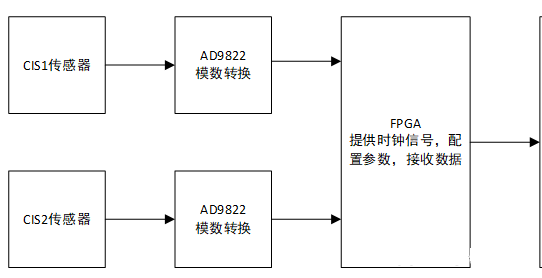

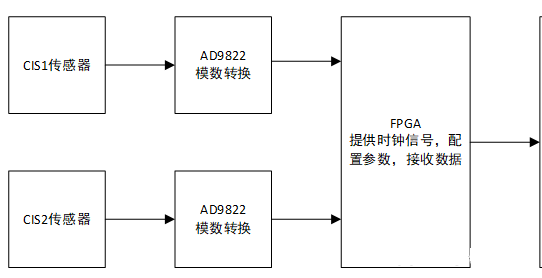

通過使用線性圖像傳感器CIS采集的圖像判斷產線上的鋁箔是否有污點、裂痕、氣孔、褶皺等等問題,傳統是通過人眼觀察或者工業相機檢查,人眼觀察主要由于抽檢,無法做到實時監測,工業相機的問題是為了獲得足夠寬的拍攝角度,相機距離被測物體較遠,設備產生的震動、粉塵、照明光線等都會影響采集效果,而且無法做到高速檢測,鏡頭的畸變也會影響檢測效果。

選用的華菱光電CIS傳感器,分辨率為300DPI時,一行像素有3672個,采樣圖像寬度在30cm左右,這個分辨率可以采集出的圖片達到4K級別,這個是一般工業相機很難達到的。

通過使用線性圖像傳感器CIS采集的圖像判斷產線上的鋁箔是否有污點、裂痕、氣孔、褶皺等等問題,傳統是通過人眼觀察或者工業相機檢查,人眼觀察主要由于抽檢,無法做到實時監測,工業相機的問題是為了獲得足夠寬的拍攝角度,相機距離被測物體較遠,設備產生的震動、粉塵、照明光線等都會影響采集效果,而且無法做到高速檢測,鏡頭的畸變也會影響檢測效果。

選用的華菱光電CIS傳感器,分辨率為300DPI時,一行像素有3672個,采樣圖像寬度在30cm左右,這個分辨率可以采集出的圖片達到4K級別,這個是一般工業相機很難達到的。

FPGA將采集的信號通過千兆網輸出到計算機,千兆網芯片選用的是RTL8211,由于開始設計的框圖想用高速USB接口,結果由于驅動問題太麻煩,改成了千兆網進行傳輸。

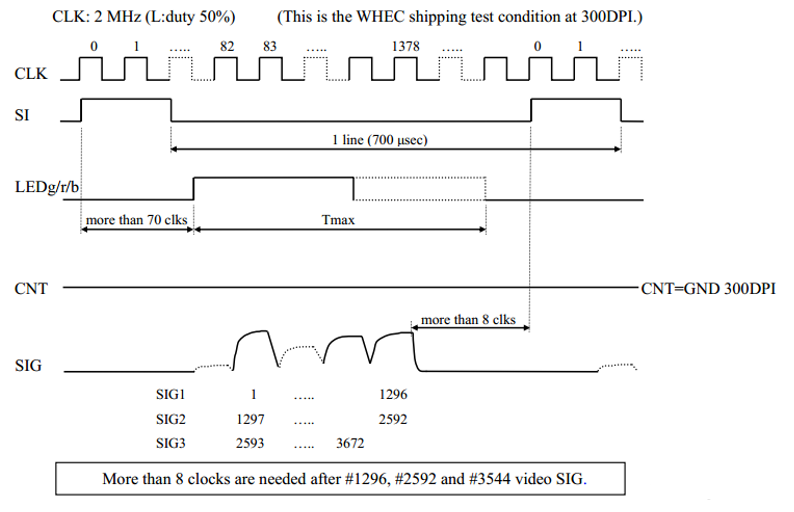

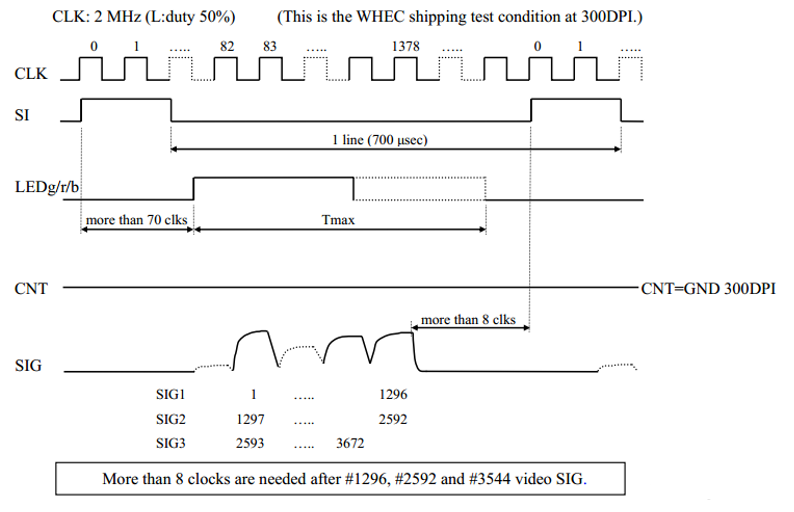

其中麻煩的地方在于數據采集的時序和圖像校正,先看一下傳感器時序圖。

FPGA將采集的信號通過千兆網輸出到計算機,千兆網芯片選用的是RTL8211,由于開始設計的框圖想用高速USB接口,結果由于驅動問題太麻煩,改成了千兆網進行傳輸。

其中麻煩的地方在于數據采集的時序和圖像校正,先看一下傳感器時序圖。

CLK:2MHz時鐘

SI:開始采集信號

LEDg/r/b:傳感器自帶RGB三色補光燈

SIG:傳感器輸出的模擬信號,分為三段,相當于一根傳感器是三個傳感器組成的

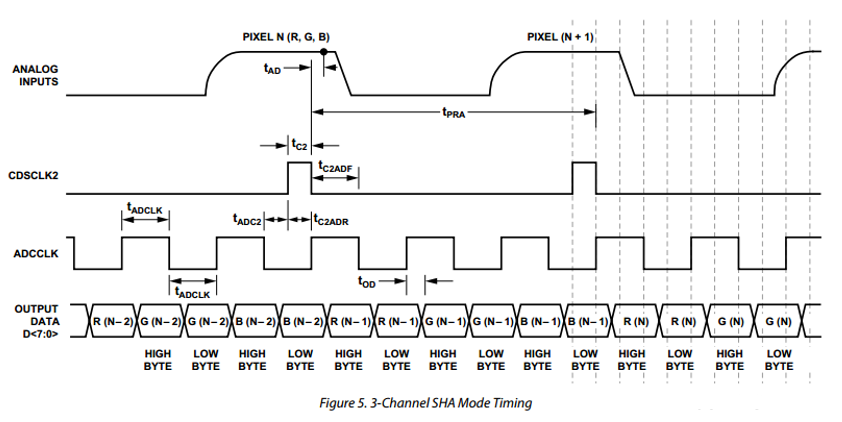

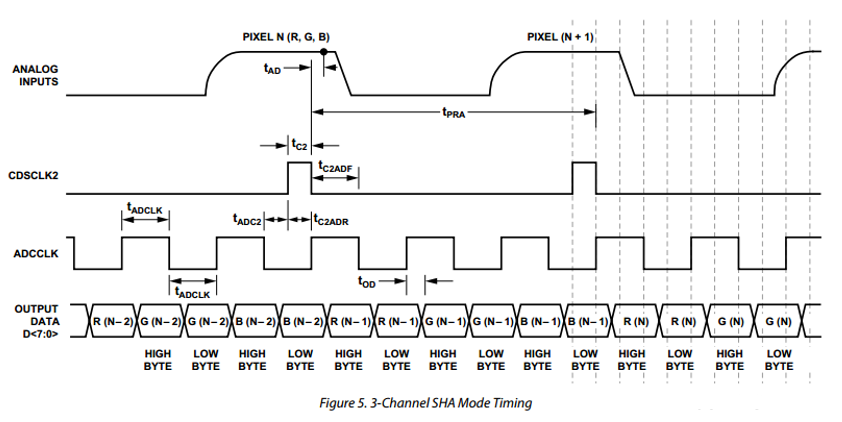

ADC采集芯片選用的是AD9822,這個芯片主要由于CCD/CIS的圖像采集,性能優秀,下面是時序圖,芯片也是分3通道采集,可以對應RGB通道。

CLK:2MHz時鐘

SI:開始采集信號

LEDg/r/b:傳感器自帶RGB三色補光燈

SIG:傳感器輸出的模擬信號,分為三段,相當于一根傳感器是三個傳感器組成的

ADC采集芯片選用的是AD9822,這個芯片主要由于CCD/CIS的圖像采集,性能優秀,下面是時序圖,芯片也是分3通道采集,可以對應RGB通道。

CDSCLK2:采樣點

ADCCLK:ADC數據輸出時鐘(由CPLD提供,同時采樣3通道,即頻率為采樣點的3倍)

OUTPUTDATA:并行輸出數據

我們用來采集傳感器的3個部分,經過AD轉換后在進行數據重新排序和拼接。

在3通道SHA模式下,AD9822同時采樣SIG1,SIG2和SIG3輸入電壓。采樣點由CDSCLK2控制。 CDSCLK2的下降沿對每個通道上的輸入波形進行采樣[A1] 。來自三個SHA的輸出電壓由DAC修改,然后由三個PGA縮放。然后PGA的輸出通過14位ADC多路復用。 ADC在ADCCLK的下降沿順序采樣PGA輸出。

OFFSET引腳可以用作粗偏置調整引腳。在AD9822的一級放大器中,從施加到SIG1,SIG2和SIG3輸入的電壓中減去施加到該引腳的電壓。在這種模式下,輸入鉗位被禁用。有關更多信息,請參見電路操作部分。

CDSCLK1應在該模式下接地。盡管不是必需的,但建議CDSCLK2的下降沿與ADCCLK的上升沿同時發生或在ADCCLK的上升沿之前發生。如tADC2所示,CDSCLK2的上升沿不應出現在先前的ADCCLK下降沿之前。輸出數據等待時間為三個ADCCLK周期。

SIG1,SIG2和SIG3通道的偏移和增益值是使用串行接口編程的。通過對MUX寄存器進行編程,可以選擇通過多路復用器切換通道的順序。

PGA,offset參數需要根據測試結果調節,可以先設置為最小,逐漸增加。

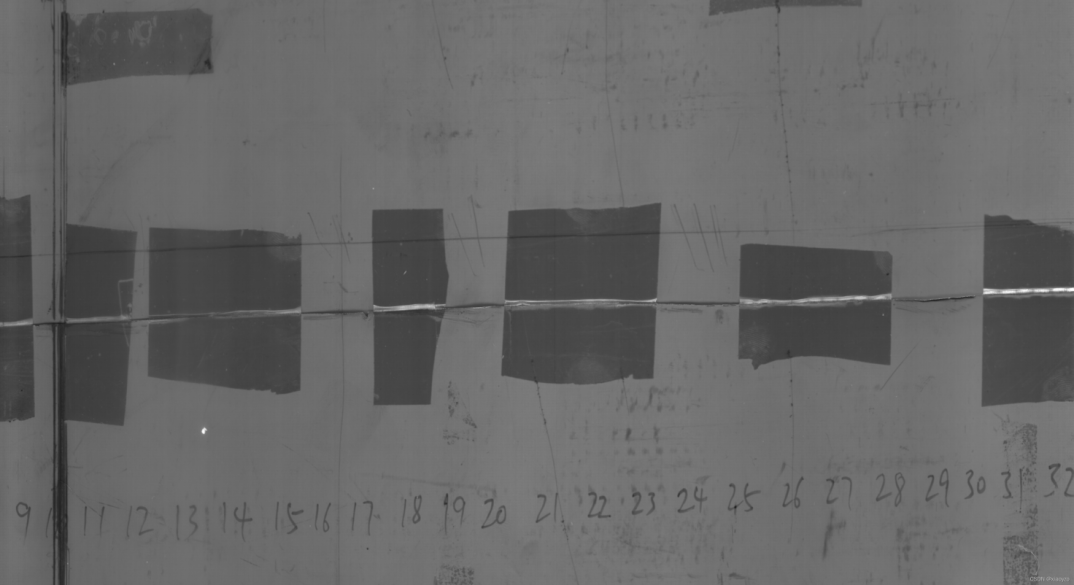

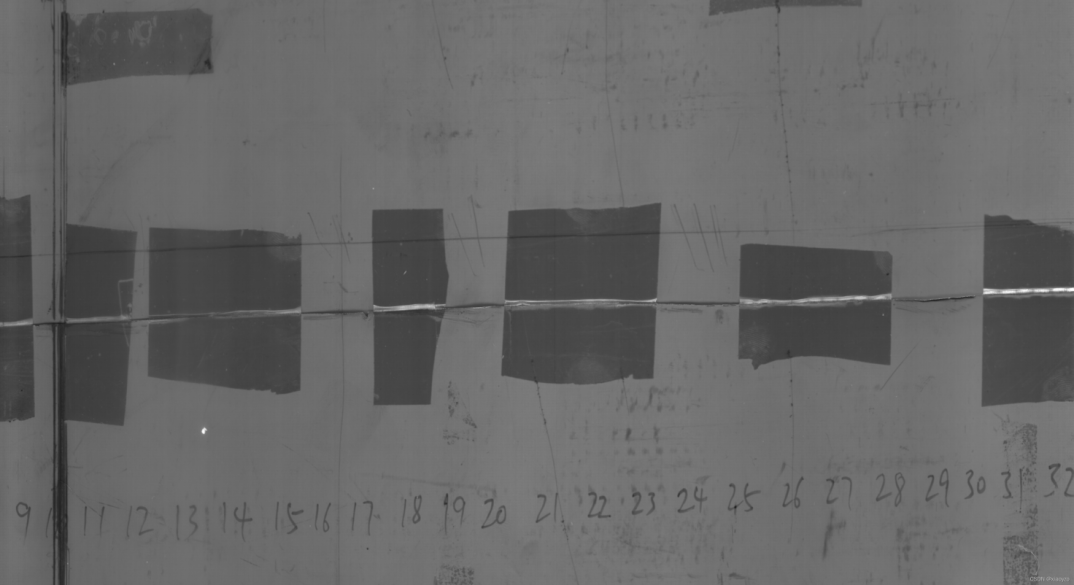

采樣效果如下:

CDSCLK2:采樣點

ADCCLK:ADC數據輸出時鐘(由CPLD提供,同時采樣3通道,即頻率為采樣點的3倍)

OUTPUTDATA:并行輸出數據

我們用來采集傳感器的3個部分,經過AD轉換后在進行數據重新排序和拼接。

在3通道SHA模式下,AD9822同時采樣SIG1,SIG2和SIG3輸入電壓。采樣點由CDSCLK2控制。 CDSCLK2的下降沿對每個通道上的輸入波形進行采樣[A1] 。來自三個SHA的輸出電壓由DAC修改,然后由三個PGA縮放。然后PGA的輸出通過14位ADC多路復用。 ADC在ADCCLK的下降沿順序采樣PGA輸出。

OFFSET引腳可以用作粗偏置調整引腳。在AD9822的一級放大器中,從施加到SIG1,SIG2和SIG3輸入的電壓中減去施加到該引腳的電壓。在這種模式下,輸入鉗位被禁用。有關更多信息,請參見電路操作部分。

CDSCLK1應在該模式下接地。盡管不是必需的,但建議CDSCLK2的下降沿與ADCCLK的上升沿同時發生或在ADCCLK的上升沿之前發生。如tADC2所示,CDSCLK2的上升沿不應出現在先前的ADCCLK下降沿之前。輸出數據等待時間為三個ADCCLK周期。

SIG1,SIG2和SIG3通道的偏移和增益值是使用串行接口編程的。通過對MUX寄存器進行編程,可以選擇通過多路復用器切換通道的順序。

PGA,offset參數需要根據測試結果調節,可以先設置為最小,逐漸增加。

采樣效果如下:

由于被測物體時灰色,一般工業攝像機都很難看清細節,比如微小的劃痕和裂縫,但是華菱光電的CIS傳感器就可以很好的捕捉到各種細節。

由于被測物體時灰色,一般工業攝像機都很難看清細節,比如微小的劃痕和裂縫,但是華菱光電的CIS傳感器就可以很好的捕捉到各種細節。

魯ICP備09100748號-2

魯ICP備09100748號-2